生产集成电路的第一步是通过掩模向基底透射电路图案。光敏性聚合物光刻胶经紫外线曝光后,受照射部分通过显影作用去除。一旦电路图案在光刻胶上定型后,即可通过刻蚀工艺将图案复制到多晶硅等质地的基底薄膜上,从而形成晶体管门电路,同时用铝或铜实现元器件之间的互连,或用二氧化硅来阻断互连路径。刻蚀的作用在于将印刷图案以极高的准确性转移到基底上,因此刻蚀工艺必须有选择地去除不同薄膜,基底的刻蚀要求具备高度选择性。否则,不同导电金属层之间就会出现短路。另外,刻蚀工艺还应具有各向异性,那样可保证将印刷图案精确复制到基底上。

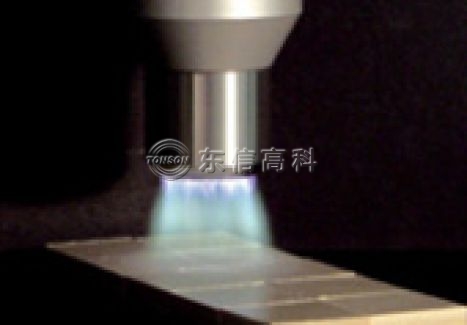

20世纪70年代,微电子元器件产业开始采用等离子刻蚀技术。等离子体可将气体分子离解或分解为化学活性组分,后者与基底的固体表面发生反应,生成挥发性物质,然后被真空泵抽走。通常有四种材料必须进行刻蚀处理:硅(惨杂硅或非惨杂硅)、电介质(如SiO2或SiN)、金属(通常为铝、铜)以及光刻胶。每种材料的化学性质都各不相同。等离子体刻蚀为一种各向异性刻蚀工艺,可以确保刻蚀图案的精确性、对特定材料的选择性以及刻蚀效果的均匀性。等离子体刻蚀中,同时发生着基于等离子作用的物理刻蚀和基于活性基团作用的化学刻蚀。等离子体刻蚀工艺始于比较简单的平板二极管技术,已经发展到时用价值数百万美元的组合腔室,配备有多频发生器、静电吸盘、外部壁温控制器以及针对特定薄膜专门设计得多种流程控制传感器。

可进行刻蚀处理的电介质为二氧化硅和氮化硅。这两种电介质的化学键键能很高,一般需采用由碳氟化合物气体(如CF4、C4F8等)产生的高活性氟等离子体才能将其刻蚀。上述气体所产生的等离子体化学性质极为复杂,往往会在基底表面产生聚合物沉积,一般采用高能离子将上述沉积物去除。